COMP 3511: Lecture 18

Date: 2024-11-05 14:24:18

Reviewed:

Topic / Chapter:

summary

❓Questions

Notes

Segmentation

-

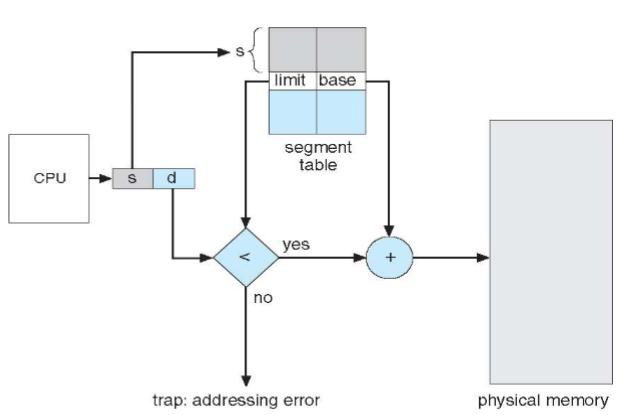

Segmentation architecture

- logical address: consists of

two-tuple- segment-number, offset

- segment table: maps 2D programmer-defined address into 1D physical address

- each entry: contains:

base: containing starting physical address of each segmentlimit: specifying length of segment

- each entry: contains:

- both STBR / STLR: stored in PCB of a process

- segment-table base register (STBR): points to segment table's location in memory

- segment-table length register (STLR): indicating no. of segments used by program

- segment no. : legal if

- protection: each entry in segment table associating w/

validation bit = 0: illegal segment- 👨🏫 part of protection bit

- read / write / execute privileges

- protection bit: associated w/ each segment

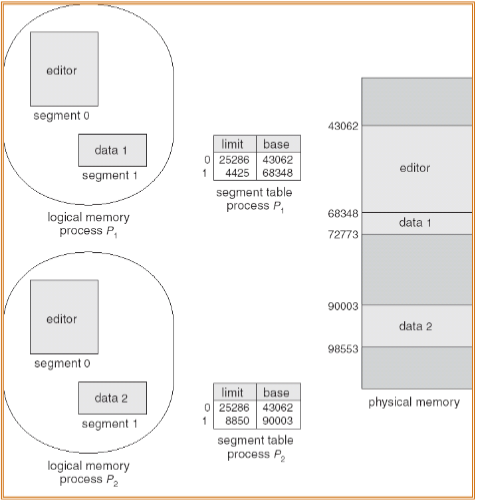

- code sharing: occurring at segment level

- each segment: vary in length

- thus dynamic storage allocation problem still exists

- yet, much less severe as each segment: considerably smaller than entire memory space

- process: might share data

- simply use same base & limit in segmentation table for shared segment!

- logical address: consists of

-

Summary segmentation

- protection: easy in segment table

- code segment: read-only

- data & stack: read-write, etc.

- address: can be outside valid range

- as stack & heap: allowed to grow

- system automatically increase the size of stack

- main program w/ segmentation

- dynamic storage allocation problem and external fragmentation persists

- may move processes multiple times to fit everything

- from processor view: good & easy

- protection: easy in segment table

Paging

-

Paging

- divide physical memory into fixed-sized blocks: frames

- usually power of 2: between

4 KB(12 bit offset) to1 GB(30 bit offset)- defined by the hardware

- 👨🏫 frame number: unique in physical address

- usually power of 2: between

- divide logical memory into: blocks of same-size pages (same size as frame)

- OS: keep track of all free (physical) frames available in main memory

- to run program of size pages: find free frames (non-contiguous) in memory

- page table: used for translating logical to physical address

- yet: suffers from internal fragmentation in last page / frame

- divide physical memory into fixed-sized blocks: frames

-

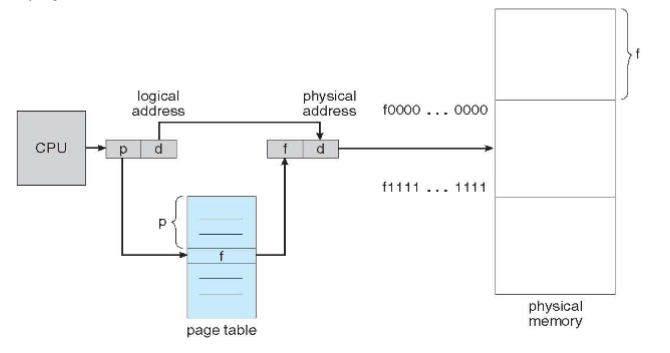

Address translation scheme

- address generated by CPU: 2 parts

- page number (p): index for page table

- containing base address of each page in physical memory

- page offset (d): combined w/ base address to define physical memory

- page number (p): index for page table

page number page offset - page size / frame size: fixed

- same for size of page

- for bits logical address, logical address space: bytes

- if page size / frame size

- no. of pages:

- example

- let page no. -bit, page off set -bit

- then page size: KB

- 32 bit virtual address: shows GB

- 20 bits for page no.: no. of pages

- address generated by CPU: 2 parts

-

Paging hardware

- steps:

- extract page no. and use it for page table index

- extract corresponding frame no. from page table

- replace page no. with frame no.

- offset : doesn't change, but replaced

- frame no. & offset: not gives physical address

- steps:

-

Paging example

- frame no.: automatically derive from starting address of each frame

- : means logical address of bytes

- logical address : page 0 & offset 0

- page 0 = frame 5 (from table)

- logical address 0: physical address

5<<n + 0 = 20 - logical address

3=(0,3): physical address5<<n + 3 = 23 - logical address

4=(1,0): physical address6<<n + 0 = 24 - logical address

13=(3,1): physical address2<<n + 1 = 9

- : each page size: bytes

- calculating internal fragmentation

- page size:

2,048bytes (2KB) - process size:

72,766bytes - 35 pages + 1086 bytes

- internal fragmentation:

2,048 - 1,086 = 962bytes - worst case fragmentation:

1 frame - 1 byte - average fragmentation:

1/2 frame

- page size:

- is small frame: desirable?

- page size: grown over time

- SubMicro Solaris: support 8 KB and 4 MB

- process & physical memory view: very different

- for programmer: memory is contiguous

- actually: no

- for programmer: memory is contiguous

-

Implementation of page table

- page table: in main memory

- PCB: keep track of memory allocation for process

- page-table base register (PTBR):

- page-table length register (PTLR):

- under the scheme: every data / instruction access requires two memory access

- one for page table (translation) and another for fetching data

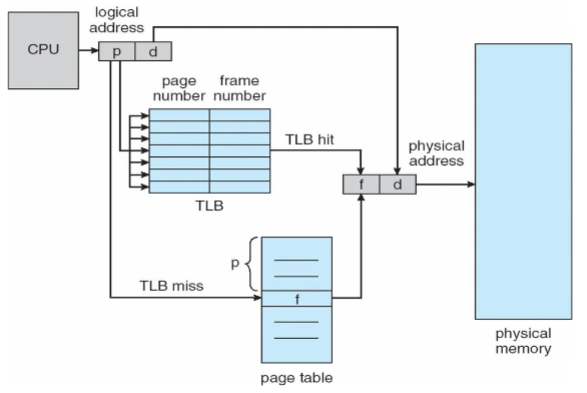

- associative memory / translation look-aside buffers

- page table: in main memory

-

Associative memory

- a parallel search

- address translation

- check all entries in parallel

- TLB: shared & used by all processes

- (w/ PID and page number)

- if : in associative register: get frame no. out: (TLB hit)

- else: bring the entry to TLB / memory

- check all entries in parallel

- locality on TLB

- instruction: usually stays on the same page (sequential access nature)

- stack: exhibits locality (pop in & out)

- data: less locality, still quite a bit

-

Paging hardware w/ TLB